## 2025 IEEE VLSI Review

서울대학교 전기정보공학부 박사과정 박현준

## Session 7 High-Density Short-Reach Links

최근 칩렛·패키징 시대의 본격화로 다이-투-다이(D2D)·포토닉·메모리 버스까지 포함한 패키지-인 인터커넥트가 시스템 성능의 병목이자 차별화 축으로 부상했다. Session 7은 Shoreline density(Tbps/mm·Gb/s/mm)와 에너지 효율(pJ/bit)을 동시에 끌어올리는 최신 흐름을 집약한다. 공정(3 nm~28 nm)·패키지(2.5D·3D)·회로·신호처리의 co-design이 핵심이며, 표준을 유지한 채 지연·전력·채널 견고성을 동시에 해결하는 솔루션을 제시한다. 결과적으로, 본 세션은 칩렛 상호운용성·스케일아웃 확장성을 뒷받침하는 회로-시스템 융합연구의 최전선을 보여주며, 차세대 AI/HPC 시스템의 대역폭/전력 한계를 갱신하는 실질적 로드맵을 제시한다.

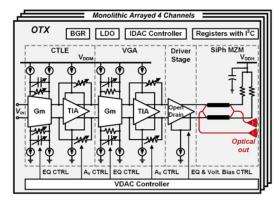

#7-1 본 논문은 45-nm SOI CMOS에서 전자-광 소자를 집적한 4×112-Gb/s Si-photonic 트랜시버를 제안한다. 핵심은 (i) TW-MZM과 고스윙 오픈드레인 드라이버의 co-design으로 선로/패키지 기생을 최소화하며 33.1 GHz 대역폭을 확보하고, (ii) 단일-스테이지 인버터형 TIA에 분산 다중노드 인덕티브 피킹을 적용해 PD 응답과 동시 최적화, 39.8 GHz와 저잡음을 달성한 점이다. 이 원리로 고밀도·저전력을 동시에 실현하여 112 Gb/s PAM-4에서 OTX 2.36 pJ/bit·224 Gb/s/mm, ORX 1.15 pJ/bit·299 Gb/s/mm를 기록했고, RLM 0.972로링크 타당성을 검증하였다.

[7-1] OTX & ORX block diagram.

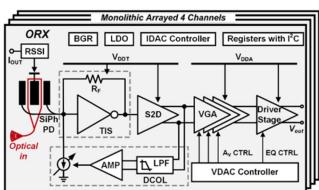

#7-2 본 논문은 3 nm FinFET에서 UCle Standard Package(SP) 규격을 만족하는 16 Gb/s/pin ×16 D2D PHY를 제안한다. 핵심은 (i) TX 클록 정렬을 Pl(phase interpolator)로

직접 맞추는 CDC로 FIFO 없이 인터페이스를 닫아 FDI-to-FDI 지연 4.0 ns를 달성하고, (ii) 클록 포워딩·지연매칭 아키텍처와 DCD(듀티 왜율) 백그라운드 보정을 결합해 VT 드리프트에도 eye-opening을 +0.156 UI 개선하며, (iii) 단일-엔디드 NRZ + 듀얼 스윙(HS/LS) 드라이버로 shoreline density와 전력 효율을 동시에 끌어올린 점이다. 이 설계로 130 μm 피치 SP에서 0.448 Tb/s/mm와 0.52 pJ/bit를 달성했고, 25 mm 유기기판 채널에서 16 Gb/s/pin 동작 시 BER=1e-15에서 0.372 UI, 1e-27에서 0.108 UI의 종합 아이를 확인하였다. 결과적으로, 저지연·저전력·고밀도라는 UCle SP의 3대 요구를 표준 패키지에서 동시에 만족하며, 실사용 환경의 전압·온도 변동까지 견딜 수 있음을 시스템 레벨로 입증했다.

[7-2] (좌) (a) Top level block diagram of the UCIe-SP module, (b) bump map of the UCIe-SP module

[7-3] ( $\Re$ ) 3D chip-stacking decreases bond pitch from 50  $\mu m$  to less than 10  $\mu m$  and needs new die-to-die links that are small, energy efficient, low latency, and high bandwidth.

#7-3 본 논문은 3 nm에서 PLL과 FIFO 없이 한 번의 상승 에지로 4 bit/pin을 직렬화·전송·역직렬화하는 자기 타이밍(self-timed) D2D 링크를 제안한다. 핵심은 (i) 저펄스 체인 →SR-래치 조합으로 TX CLK과 Forwarding용 CLK을 생성해 전송 UI의 정중앙에 포워드 클록을 보장하고, 총 지연을 디지털 임계 경로와 매칭해 전압 노이즈·DVFS·PVT 변화에 자동 추종하게 한 점, (ii) 링크 전 경로가 TX 디지털 클록 도메인과 동기되어 CDC/FIFO 없이 단일-사이클(링크 내부는 zero-cycle) 지연을 달성한 점, (iii) valid 게이팅으로 사이클 단위로 고속 클록을 정지시켜 활동도에 비례해 전력을 줄이는 완전 디지털풀스윙 구조다. 이 원리로 복잡한 클록 생성·보정 회로를 제거하면서 회로 면적을 미세 본딩 피치 (<5μm 대응)까지 축소해 밀도 이득을 확보했다. 측정 결과 16-lane(64 bit) 링크가 8 Gb/s/pin, 77 fJ/bit @0.7 V, 44 Tb/s/mm²를 달성했고, 1-사이클 레이턴시와 넓은 전압·주 파수 범위에서의 무오류 동작 및 여유(setup/hold 마진 주입 측정)를 보였다. 결론적으로, 단순·소형 표준셀 기반의 자기 타이밍 직렬화로 2.5D/3D 인터커넥트에서 저전력·저지연·초고밀도를 동시에 실현했다.

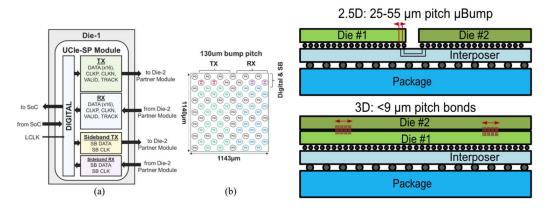

#7-4 본 논문은 16 nm FinFET에서 NRZ 시그널링을 유지하면서 TX 3-tap FFE + RX 랜덤 포레스트 분류기로 장거리 ISI를 보상하는 25 Gb/s 링크를 제안한다. 핵심은 (i) RX가 3개 임계(비교기)로 뽑은 1-bit 1차 특징들을 여러 UI로 묶어 채널의 프리/메인/포스트 커서를 표현하고, (ii) 이를 오프칩 학습→온칩 합성된 랜덤포레스트가 결정 트리 다수결로 복원함으로써, (iii) 복잡한 다탭 EQ나 특수 인코딩 없이 3-tap FFE만으로도 대손실 채널(30-47 dB)을 커버하도록 만든 점이다. 저속 도메인에 분류기를 배치해 전력(분류기 9%)을 억제하고, AFE는 4단 증폭+인덕티브 피킹으로 대역을 확보한다. 이 원리로 추가 전압레벨/디코딩 없이 표준 NRZ 호환을 유지하며 전력-효율을 탭 수 증가보다 우선 최적화했고, 측정 결과 25 Gb/s에서 BER<1e-11, 3.2 pJ/b, 채널 손실당 0.068 pJ/b/dB, 링크 지연 10 UI로 47 dB 손실을 보상함을 입증했다.

[7-4] Machine learning inspired wireline transceiver concept with feature extraction and random forest classification.

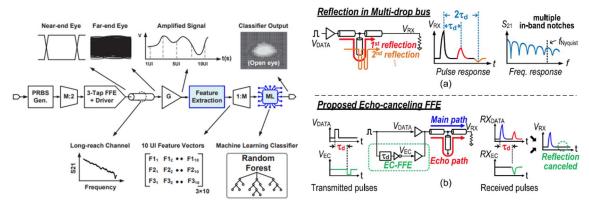

[7-5] (a) Reflection in a multi-drop bus channel, and (b) the concept of the proposed echo canceling FFE.

#7-5 본 논문은 28 nm에서 멀티드롭 버스(MDB)의 반사 에코를 송신단에서 선제적으로 상쇄하는 에코-캔슬링 FFE(EC-FFE) 기반 12 Gb/s 단일종단 TX를 제안한다. 핵심은 (i) 반사 지연마다 스케일·부호를 조절한 EC 펄스 열을 송신해 원펄스의 고차 에코까지 누적 상쇄하고, (ii) 에코가 더 넓어지는 채널-의존 파형 왜곡을 EC 탭의 2-tap FFE로 펄스-셰이 핑해 모양까지 일치시키는 점이다. 이를 위해 N-UI 지연체인 + VCDL의 이단 지연 구조 (탭 k당 k-stage VCDC, 공용 바이어스)로 정수·분수 UI 지연을 정밀 매칭하여 다양한 스텁 길이(8-12 cm)에 대응한다. 그 결과, 다중 대역노치 MDB(10 dB @ Nyq, 8개 노치)에서 반사 제거→아이 복원(EC-FFE만: 15.8 mV/0.4 UI → 펄스-셰이핑 포함: 30.5 mV/0.62 UI), BER < 1e-12에서 0.29 UI, 1.52 pJ/b, 면적 0.01 mm²를 달성했다. 즉, NRZ·단일종단을 유지 하면서 지연·스케일·파형을 동시 최적화해, 복잡한 수신 DFE나 비표준 변조 없이 반사성 채널을 저전력으로 보상한다.

## 저자정보

## 박현준 박사과정 대학원생

● 소속 : 서울대학교

● 연구분야 : 수학

● 이메일 : spp098@snu.ac.kr